Project information

- Category: Processor

- UE: Calculator structure

- Project date: Semester 5, 2023

- Project code: Github

- Technology: Python and Logisim

Project description :

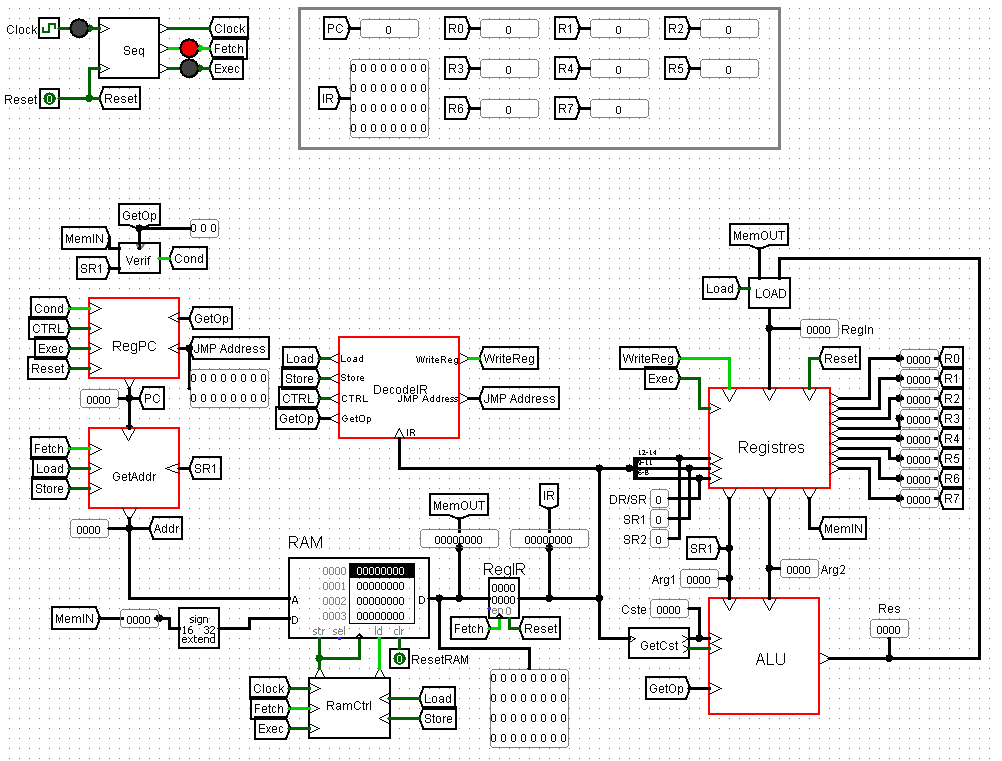

I carried out this project using logisim and python in collaboration with Nicolas GALLET, Maxime ANTOINE and Dorian TONNIS. The aim of the project is to implement a circuit modelling a processor, which will be able to perform the following instructions: ADD, SUB, AND, OR, XOR, SL, SR (and their immediate variants), STR, LD, JMP, JEQU, JNEQ, JSUP, JINF, CALL and RET. The processor has the following characteristics: 16 × 32 memory, i.e. storing 216 words of 32 bits, 8 working 16-bit registers R0,...,R7, two special registers: IR (32 bits) and PC (16 bits), each instruction cycle is divided into two phases: Fetch and Exec . Each of these phases lasts one clock cycle. In addition, we have a python program for translating assembly code into machine code (the contents of the memory).